Page 1 of 2

Help with XC compiler problem

Posted: Fri Jan 22, 2021 9:11 pm

by wayne_millard

To all,

I have a problem compiling a project that was made in flowcode6 and now trying to compile in flowcode9 and have the following problems any help would be great.

FCM_RS232_Rx()

9803: if ((rcsta & (1 << FERR)) != 0)

^ (192) undefined identifier "rcsta"

9805: dummy = rcreg;

^ (192) undefined identifier "rcreg"

9814: FCV_RX_BUFF[FCV_RX_BUFF_END] = rcreg;

^ (192) undefined identifier "rcreg"

c: main()

12468: pie1.RCIE=1;

^ (192) undefined identifier "pie1"

^ (196) struct/union required

12469: intcon.PEIE = 1;

^ (192) undefined identifier "intcon"

^ (196) struct/union required

12470: rcsta |= (1 << CREN);

^ (192) undefined identifier "rcsta"

12471: intcon.GIE = 1;

^ (196) struct/union required

c: myisr()

13554: if(pir1 & (1 <<RCIF))

^ (192) undefined identifier "pir1"

(908) exit status = 1

(908) exit status = 1

Thanks,

Wayne Millard

Re: Help with XC compiler problem

Posted: Fri Jan 22, 2021 9:37 pm

by kersing

Take a look at your C code icons. If you need help it would be best to post the code from them as code block on the forum in stead of having us try to distil th8ngs from the compiler errors.

Re: Help with XC compiler problem

Posted: Fri Jan 22, 2021 9:41 pm

by medelec35

Hi Wayne.

FC6 uses boost C which uses lower case for register names.

FC7 and above changed to XC8 which uses upper case for register names.

You will also require a different format.

Eg. instead of

Use

For

Code: Select all

FCV_RX_BUFF[FCV_RX_BUFF_END] = rcreg;

use

Code: Select all

FCV_RX_BUFF[FCV_RX_BUFF_END] = RCREG;

ect.

Re: Help with XC compiler problem

Posted: Sat Jan 23, 2021 12:33 am

by wayne_millard

Hi Martin,

Thanks for the feed back i have now changed all that you said and now have this problem.

12468: PIE1.RCIE=1;

^ (196) struct/union required

12469: INTCON.PEIE = 1;

^ (196) struct/union required

12471: INTCON.GIE = 1;

^ (196) struct/union required

(908) exit status = 1

(908) exit status = 1

Thanks for the help.

Wayne Millard

Re: Help with XC compiler problem

Posted: Sat Jan 23, 2021 1:55 am

by medelec35

You're welcome.

Yes you will have an issue.

Its to do with

medelec35 wrote: ↑Fri Jan 22, 2021 9:41 pm

Eg. instead of

intcon.PEIE = 1;

Use

st_bit(INTCON,PEIE);

The format of

will not work.

Best to use the format of

so you will need to use

instead of

Re: Help with XC compiler problem

Posted: Sat Jan 23, 2021 1:33 pm

by wayne_millard

Hi Martin,

Thanks for your great help.

Wayne Millard

Re: Help with XC compiler problem

Posted: Sat Jan 23, 2021 2:29 pm

by medelec35

Hi Wayne,

All sorted now?

I have just remembered another way.

I stated

will not work.

However if you place a lower case

after the register name e.g REGISTERbits.BIT = value;

It will work .

for example, you can use

Other things to note.

You can clear bits with cr_bit instead of st_bit.

If the bit name has a bar above it like this:

- NOTbit.png (36.81 KiB) Viewed 17634 times

The you must precede the bit name with a lower case n.

So to enable weak pull-ups on PIC16F1825 for example, you can use

or

Re: Help with XC compiler problem

Posted: Fri Jun 24, 2022 7:28 am

by jan.didden

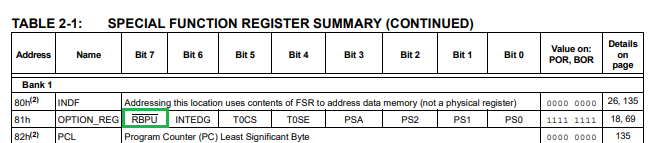

This had stumped me some time: how to name a bit called (overbar)WPPU in the data sheet.

Of course: OPTION_REGbits.nWPPU = 1 !

Thanks (again) Martin.

Jan Didden

Re: Help with XC compiler problem

Posted: Fri Jun 24, 2022 8:45 am

by medelec35

Hi Jan.

You're welcome.

Microchip does not make it that easy to work out.

Thanks for letting me know I have helped.

Re: Help with XC compiler problem

Posted: Fri Jun 24, 2022 9:44 am

by BenR

Hello,

If you ever need to know the specifics for a PIC device then the easiest way is to look at the .h file in the compiler pic/include/ directory.

For example for the 16F877A I looked at the pic16F877a.h file.

Then search the file for the register your interested in, here is the section for the OPTION_REG register.

Code: Select all

#define OPTION_REG OPTION_REG

extern volatile unsigned char OPTION_REG @ 0x081;

#ifndef _LIB_BUILD

asm("OPTION_REG equ 081h");

#endif

// bitfield definitions

typedef union {

struct {

unsigned PS :3;

unsigned PSA :1;

unsigned T0SE :1;

unsigned T0CS :1;

unsigned INTEDG :1;

unsigned nRBPU :1;

};

struct {

unsigned PS0 :1;

unsigned PS1 :1;

unsigned PS2 :1;

};

} OPTION_REGbits_t;