Difference between revisions of "Component: SPI Master (Comms: Interface)"

| Line 15: | Line 15: | ||

Low level routines for controlling or interacting with an SPI interface. SPI or Serial Peripheral Interface is a bus used for board level communications between devices. A target microcontroller will usually have at least one hardware SPI peripheral built in. If the hardware SPI pins are in use or more SPI channels are required then there is also a software mode available. | Low level routines for controlling or interacting with an SPI interface. SPI or Serial Peripheral Interface is a bus used for board level communications between devices. A target microcontroller will usually have at least one hardware SPI peripheral built in. If the hardware SPI pins are in use or more SPI channels are required then there is also a software mode available. | ||

| − | ==Component | + | ==Component Source Code== |

| − | + | Please click here for the component source code: [https://www.flowcode.co.uk/wikicopy/componentsource/FC_Comp_Source_SPI_Master.fcfx FC_Comp_Source_SPI_Master.fcfx] | |

==Detailed description== | ==Detailed description== | ||

| + | |||

| + | |||

| Line 63: | Line 65: | ||

==Examples== | ==Examples== | ||

| + | |||

| + | |||

| Line 300: | Line 304: | ||

|- | |- | ||

|- | |- | ||

| − | + | | width="10%" align="center" style="background-color:#EAE1EA;" | [[File:Fc9-conn-icon.png]] | |

| − | + | | width="90%" style="background-color:#EAE1EA; color:#4B008D;" | Connections | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | | width="10%" align="center" style="background-color:# | ||

| − | | width="90%" style="background-color:# | ||

|- | |- | ||

|- | |- | ||

| Line 354: | Line 338: | ||

| colspan="2" | Chip Select / Slave Select Pin Master Mode: General purpose output pin used to select the remote SPI device. Slave Mode: Hardware chip select pin input used to select the SPI device. | | colspan="2" | Chip Select / Slave Select Pin Master Mode: General purpose output pin used to select the remote SPI device. Slave Mode: Hardware chip select pin input used to select the SPI device. | ||

|- | |- | ||

| − | | width="10%" align="center" style="background-color:# | + | | width="10%" align="center" style="background-color:#EAE1EA;" | [[File:Fc9-conn-icon.png]] |

| − | | width="90%" style="background-color:# | + | | width="90%" style="background-color:#EAE1EA; color:#4B008D;" | Bus Settings |

| + | |- | ||

| + | |- | ||

| + | | width="10%" align="center" | [[File:Fc9-type-16-icon.png]] | ||

| + | | width="90%" | Prescale | ||

| + | |- | ||

| + | | colspan="2" | Prescale option selector | ||

| + | |- | ||

| + | | width="10%" align="center" | [[File:Fc9-type-16-icon.png]] | ||

| + | | width="90%" | Clock Phase | ||

| + | |- | ||

| + | | colspan="2" | Clock Phase (data change edge) selection | ||

| + | |- | ||

| + | | width="10%" align="center" | [[File:Fc9-type-16-icon.png]] | ||

| + | | width="90%" | Clock Polarity | ||

| + | |- | ||

| + | | colspan="2" | Clock Polarity setting, inactive (idle) state | ||

| + | |- | ||

| + | | width="10%" align="center" | [[File:Fc9-type-16-icon.png]] | ||

| + | | width="90%" | Sample Point | ||

| + | |- | ||

| + | | colspan="2" | Data bit read sample point | ||

| + | |- | ||

| + | | width="10%" align="center" style="background-color:#EAE1EA;" | [[File:Fc9-conn-icon.png]] | ||

| + | | width="90%" style="background-color:#EAE1EA; color:#4B008D;" | Simulation | ||

|- | |- | ||

|- | |- | ||

Revision as of 17:50, 9 November 2022

| Author | Matrix Ltd |

| Version | 2.1 |

| Category | Comms: Interface |

Contents

SPI Master component

Low level routines for controlling or interacting with an SPI interface. SPI or Serial Peripheral Interface is a bus used for board level communications between devices. A target microcontroller will usually have at least one hardware SPI peripheral built in. If the hardware SPI pins are in use or more SPI channels are required then there is also a software mode available.

Component Source Code

Please click here for the component source code: FC_Comp_Source_SPI_Master.fcfx

Detailed description

Overview

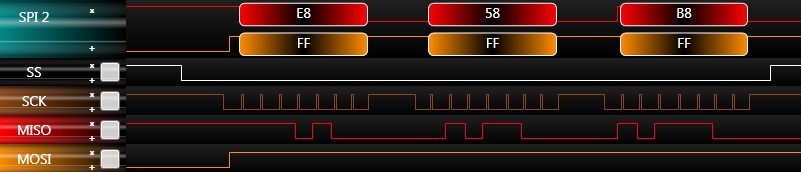

The SPI bus is a high speed communications bus which is usually best suited for talking between devices situated on the same circuit board. Due to the high frequency digital nature of the bus care should be taken to keep tracks as short as possible and as far away as possible from other sources of noise. A typical SPI bus consists of four signals, chip select, data out, data in and clock. The SPI bus usually consists of a single master device and then one or more slave devices.

As the data out and data in signals are subjective in terms of who is sending and receiving the data there are alternate names to help clarify the connection.

Data out (SDO) is also known as MOSI which stands for Master Out Slave In.

Data in (SDI) is also known as MISO which stands for Master In Slave Out.

Each SPI transaction consists of a byte made up of 8 clock cycles allowing the 8-bits of the byte to be transferred.

Chip Select CS / Slave Select SS

Each device connected to the SPI bus connects in parallel to the main three SPI pins: data out, data in and clock. The fourth pin the CS pin must be unique for every SPI device present on the bus allowing only one device to be addressed at any one time. As every slave device on the SPI bus requires a individual CS signal from the SPI Master a good way of adding more devices without consuming more of the pins of the SPI master is to use things like 3 to 8 pin multiplexer ICs. The CS signal activates the slave device when pulled low and disables the slave device when pulled high.

Adding a pull up resistor of around 10K - 100K between the CS signal and VCC allows the SPI slave device to be disabled whenever the Microcontroller is not ready to perform the functionality of the SPI master e.g. during reprogramming or when the device is held in reset.

Three Wire SPI

Three wire SPI is a version of SPI where the master can send data to the slave device but cannot read any data back for example a DAC or graphical LCD.

Four Wire SPI

Four wire SPI is the complete version of SPI where the master can sent data to the device and receive data back from the device. A single SPI operation simultaneously transfers a byte from the master to the slave via the MOSI signal and also a byte from the slave to the master via the MISO signal. Normally only one of these bytes is meaningful so it's down to the protocol of the slave device as to how to perform writes and reads.

Examples

More information on SPI can be found here,

Matrix Flowcode Blog: Simplified communications I2C and SPI

Downloadable macro reference

| SendString | |

| Sends a string of bytes to the SPI bus. Not compatible with NULL values. | |

| Str | |

| Data string to send out. | |

| Return | |

| SendChar | |

| General purpose SPI send byte macro | |

| Char | |

| Data byte to send | |

| Return | |

| Transaction | |

| Allows simultaneous two way communications, send and receive, | |

| DataOut | |

| Data Byte to send out | |

| Return | |

| Disable_CS | |

| Outputs a high signal to the chip select pin to deselect the remote slave device. | |

| Return | |

| GetChar | |

| General purpose SPI get byte macro | |

| Return | |

| UnInitialise | |

| Deactivates the SPI peripheral leaving the I/O pins in a state where they can be used for general purpose I/O. | |

| Return | |

| Enable_CS | |

| Outputs a low signal to the chip select pin to select the remote slave device. | |

| Return | |

| Initialise | |

| Activates the SPI peripheral and claims control over the I/O pins. | |

| Return | |